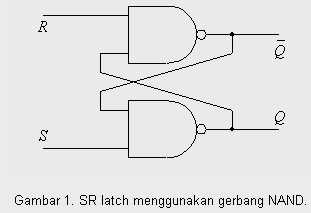

Salah satu daei jenis flip-flop adalah flip-flop RS. Flip-flop ini mempunyai dua masukan dan dua keluaran, di mana salah satu keluarannya (y) berfungsi sebagai komplemen. Sehingga flip-flop ini disebut juga rangkaian dasar untuk membangkitkan sebuah variabel beserta komplemennya. Flip-flop RS dapat dibentuk dari kombinasi dua gerbang NAND atau kombinasi dua gerbang NOR.

1. Flip Flop RS yang dibangun dari gerbang NAND

Analisis kondisi masukan dan keluaran flip-flop RS :

PERTAMA R S = 0 0

Ini berarti tidak diterapkan pemicu. Dalam hal ini keluaran y mempertahankan nilai terakhir yang dimilikinya.

KEDUA R S = 0 1

Ini berarti bahwa suatu pemicu diterapkan pada masukan S. Hal ini mengeset flip-flop dan menghasilkan keluaran y bernilai 1.

KETIGA R S = 1 0

Ini menyatakan bahwa suatu pemicu diterapkan pada masukan R. Hal ini mereset flip-flop dan menghasilkan keluaran y bernilai 0.

KEEMPAT R S = 1 1

merupakan kondisi masukan terlarang. Kondisi ini berarti menerapkan suatu pemicu pada ke dua masukan S dan R pada saat yang sama. Hal ini merupakan suatu pertentangan karena mengandung pengertian bahwa kita berupaya untuk memperoleh keluaran y yang secara serentak sama dengan 1 dan sama dengan 0. Hal ini tidak masuk akal dan oleh sebab itu masukan ini dinyatakan terlarang.

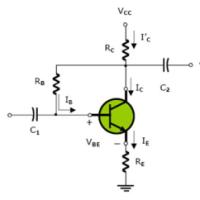

Bila clock rendah (0), ke dua gerbang AND tertutup (disabled). Hal ini menjamin bahwa : R S = 0 0 yang berarti keluaran y tetap pada keadaan terakhir yang dimilikinya. Tetapi bila clock menjadi tinggi (1), ke dua gerbang AND terbuka (enabled). Hal ini memungkinkan sinyal-sinyal S dan R mencapai flip-flop RS. Dengan cara ini, flip-flop akan set atau reset, bergantung pada nilai RS.

Oleh sebab itu, flip-flop RS ber ‘clock’ tidak dapat berubah keadaan sampai berlangsungnya sinyal clock. Penerapan clock pada sebuah flip-flop seperti di atas sangat penting dalam sistem digital berskala besar dengan beratus-ratus flip-flop yang dihubungkan satu sama lain. Clock diterapkan pada semua flip-flop secara serentak; hal ini menjamin bahwa semua flip-flop berubah keadaan pada saat yang sama. Penyerempakan ini sangat penting dalam berbagai istem digital.